The Universal Verification Methodology (UVM) has been the undisputed backbone of ASIC verification. It brought much-needed standardization, enabling the creation of robust, reusable testbenches. But as designs grew more complex, so did our verification challenges. The community yearned for updates to streamline workflows and enhance interoperability.

The wait is over. UVM 2.0 (IEEE 2023-2023) is officially here, and it’s not just a minor update—it’s a significant step forward focused on one core principle: efficiency through better reuse.

At Avecas Technologies, our verification experts live and breathe UVM. We’ve been dissecting the new standard to understand how it can accelerate our clients’ projects. Let’s break down the key improvements in UVM 2.0 and what they mean for your verification flow.

Why UVM 2.0? The Drive for a Modern Standard

The original UVM 1.2 was a triumph, but it had pain points. The phase mechanism could be rigid, integrating code from different sources sometimes led to conflicts, and the base class library had room for modernization.

UVM 2.0 addresses these issues head-on, focusing on:

- Enhanced Reuse: Making it easier to integrate VIP from different providers and reuse verification components across projects.

- Improved Debuggability: Providing clearer control and better reporting for complex testbench execution.

- Backward Compatibility: Ensuring your existing UVM 1.2 codebase continues to work, allowing for a gradual migration.

Key Features and How They Help You

Here are some of the most impactful changes in UVM 2.0:

1. The Phaser API: Taming the Synchronization Beast

This is arguably the headline feature. In UVM 1.2, synchronizing components across different domains (e.g., electronic and analog) was cumbersome, often relying on workarounds.

- What it is: The Phaser API provides a structured, explicit mechanism for coordinating the execution of tasks and functions across multiple components.

- How it improves efficiency: It offers far greater control over the order of operations. You can now precisely define barriers and synchronization points, making it much easier to integrate models that don’t naturally fit the classic UVM phase paradigm. This is a huge win for SoC-level verification and mixed-signal verification.

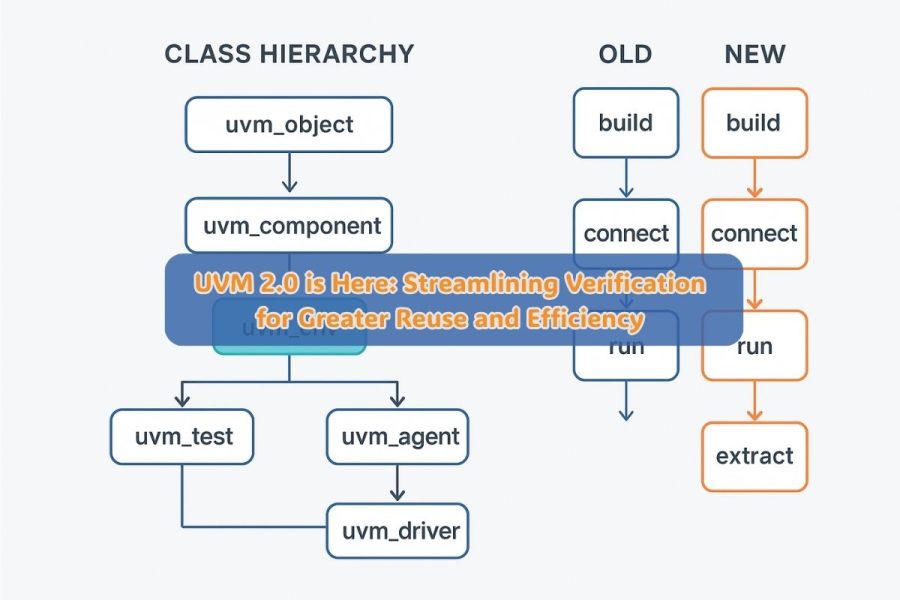

2. The New uvm_void' Root Class: Simplifying the Hierarchy

In UVM 1.2, almost everything had to inherit from uvm_object or uvm_component, even if they didn’t need all the built-in functionality like recording or factory registration.

- What it is: UVM 2.0 introduces

uvm_void'as the new abstract root class for the entire library.uvm_objectanduvm_componentnow inherit from it. - How it improves reuse: This allows you to create simpler, more lightweight classes that don’t carry the overhead of the full UVM base class. It leads to cleaner code and more efficient memory usage, especially for utility classes that don’t need full UVM features.

3. Simplified TLM Interfaces (uvm_tlm_*)

UVM 2.0 deprecates the older uvm_*_export, uvm_*_port, uvm_*_imp classes and promotes the simpler uvm_tlm_* interfaces.

- What it is: A streamlined set of TLM interfaces that are easier to use and understand.

- How it improves efficiency: This reduces the verbosity of TLM connections and minimizes the chance of connection errors. It makes assembling testbenches from reusable blocks faster and less error-prone, directly boosting productivity.

4. Command Line Processor (CLP) Enhancements

Debugging UVM testbenches often involves adding plusargs and recompiling. UVM 2.0 makes this more flexible.

- What it is: A new API allows for easier registration and querying of command line arguments within the testbench.

- How it improves debuggability: You can now create more sophisticated debug and configuration controls without hacking the code. This allows for greater runtime control over test scenarios, making the debug cycle more efficient.

5. uvm_sequence_base Class

UVM 2.0 formalizes a common practice by introducing a base class for sequences.

- What it is: The new

uvm_sequence_baseclass provides a standard foundation for all sequences. - How it improves reuse: It encourages better structure and provides a common place for future sequence-related features, making sequence libraries more consistent and portable across projects and teams.

What This Means for Your Verification Strategy

The overarching theme of UVM 2.0 is maturity and refinement. It’s about removing friction points that verification engineers face daily.

- For New Projects: Starting with UVM 2.0 is highly recommended. You’ll benefit from cleaner code, better synchronization, and a more future-proof codebase.

- For Existing Projects (UVM 1.2): You don’t need to panic. The standard maintains strong backward compatibility. You can migrate at your own pace, adopting new features like the Phaser API in specific areas where they provide immediate value.

- For VIP Integration: The standard makes it easier to combine Verification IP from different sources, reducing integration headaches and encouraging a broader ecosystem of reusable components.

Getting Started with UVM 2.0

Adopting a new standard requires expertise. At Avecas Technologies, we help our clients navigate these transitions smoothly. Our Functional Verification & Validation services are built on a deep understanding of methodologies like UVM.

Whether you need training for your team, support in migrating a legacy testbench, or want to architect a new project using the latest best practices in UVM 2.0, we have the expertise to guide you.

Ready to improve your verification efficiency and reuse? Contact Avecas today to discuss how we can help you leverage UVM 2.0 to build more robust, scalable, and efficient verification environments.