For years, the world of ASIC and SoC verification has been dominated by dynamic simulation. We build massive, complex testbenches using UVM, write thousands of tests, and run them for billions of cycles, hoping we’ve thought of every scenario. But what about the corner case you didn’t think of? The rare bug that lurks in a state only reached under a specific set of conditions that your constrained-random test never generated?

This is where Formal Verification (FV) shines. Once considered an academic or niche technique, Formal is rapidly moving into the mainstream verification flow, and for a good reason: it provides mathematical exhaustiveness. It doesn’t simulate; it proves that a design behaves correctly under all possible inputs and states.

At Avecas Technologies, we’ve integrated Formal into our core Functional Verification & Validation services. We’ve seen firsthand how it’s becoming indispensable, especially for verifying two critical areas of modern SoCs: Connectivity and Control Logic.

From Niche to Necessity: Why Formal is Going Mainstream

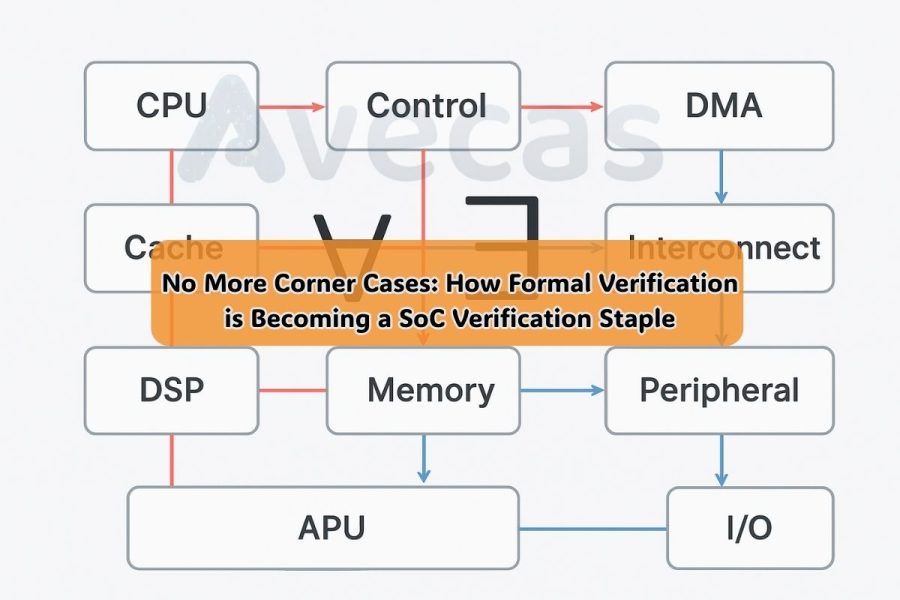

The shift is driven by sheer complexity. SoCs today are vast mosaics of IP blocks, subsystems, and power domains. The control logic and the networks that connect everything are the nervous system of the chip. A bug here can be catastrophic, causing silent data corruption or a dead system—bugs that are notoriously difficult to find and debug in simulation.

Formal verification tools have also become more powerful, user-friendly, and capable of handling larger blocks, making them accessible to more verification teams.

The Perfect Match: Formal for SoC Connectivity

SoC connectivity refers to the on-chip networks—like AMBA AXI, APB, and AHB buses—that facilitate communication between processors, memory, and peripherals.

Why is Formal a perfect fit here?

- Well-Defined Protocols: Bus protocols have clear, rules-based specifications (e.g., a write address must be held stable until a write data is accepted). These rules are easily translated into Formal properties (assertions and assumptions).

- Deadlock Detection: Formal can prove that the interconnect cannot enter a state where two masters are waiting for each other indefinitely, a bug that is incredibly time-consuming to stumble upon in simulation.

- Exhaustive Data Path Checking: You can prove that data written at one point is always correctly read at another, for all possible addresses and data patterns, something impossible to cover fully with simulation.

Using Formal for connectivity ensures that the “plumbing” of your SoC is rock-solid, providing a reliable foundation for the entire system.

Taming the Chaos: Formal for Control Logic

Control logic is the “brain” of many subsystems—finite state machines (FSMs), arbiters, power management units, and register banks. This logic is often highly state-dependent and has complex corner cases.

Formal excels here because:

- It Exhausts the State Space: Unlike simulation, which samples points in the state space, Formal explores all possible states and transitions of an FSM. It can prove that no invalid state is reachable and that every state can eventually exit.

- It Verifies Arithmetic Logic: For blocks like accelerators or DSP units, Formal can mathematically prove the correctness of arithmetic operations for all input values.

- It Simplifies Register Verification: Tools can automatically generate assertions to verify that every register in a block can be read and written correctly according to its specified access policies (RO, RW, etc.). This is far more efficient than writing manual tests for each register.

The Practical Shift: How to Integrate Formal into Your Flow

Adopting Formal doesn’t mean throwing out your simulation environment. The most effective strategy is a hybrid approach:

- Targeted Application: Don’t try to formally verify your entire CPU. Use Formal for specific, well-bounded blocks where it provides the most value: bus bridges, arbiters, FSMs, and control registers.

- Early Bug Hunting: Run Formal early in the RTL design phase. It can find deep bugs within hours of the RTL being written, when fixes are cheapest and easiest to make.

- Augmenting Simulation: Use Formal to achieve 100% coverage on control logic and then rely on simulation for the parts of the design it handles best, like complex data paths and system-level scenarios.

This is a mindset we champion in our ASIC Design and Implementation services: using the right tool for the right job to maximize efficiency and reliability.

Avecas and ChipXpert: Building Verification Expertise

The industry-wide need for Formal verification skills is growing. Our partners at ChipXpert VLSI Training Institute address this directly, ensuring the next generation of engineers is equipped with these essential skills. For seasoned professionals, mastering Formal is a key step in advancing a verification career. You can explore their curriculum to understand the foundational knowledge needed for these advanced topics on their blog.

Conclusion: Formal is No Longer Optional

The question is no longer “Should we use Formal?” but “Where can Formal help us most?” For any modern SoC, the answer is clear: start with connectivity and control logic.

Formal verification provides a level of certainty that simulation alone cannot offer. It catches the devious, corner-case bugs that evade other methods, ultimately de-risking projects and saving countless hours of debug time.

Is your verification strategy equipped for the complexity of modern SoCs? Contact Avecas Technologies today to discuss how we can integrate cutting-edge Formal verification techniques into your flow, ensuring your next design is proven correct, not just tested.