Introduction

Modern semiconductor chips are extremely complex, containing millions or even billions of transistors. Ensuring that every part of a chip works correctly after manufacturing is a major challenge. This is where Design for Testability, often called DFT, becomes essential.

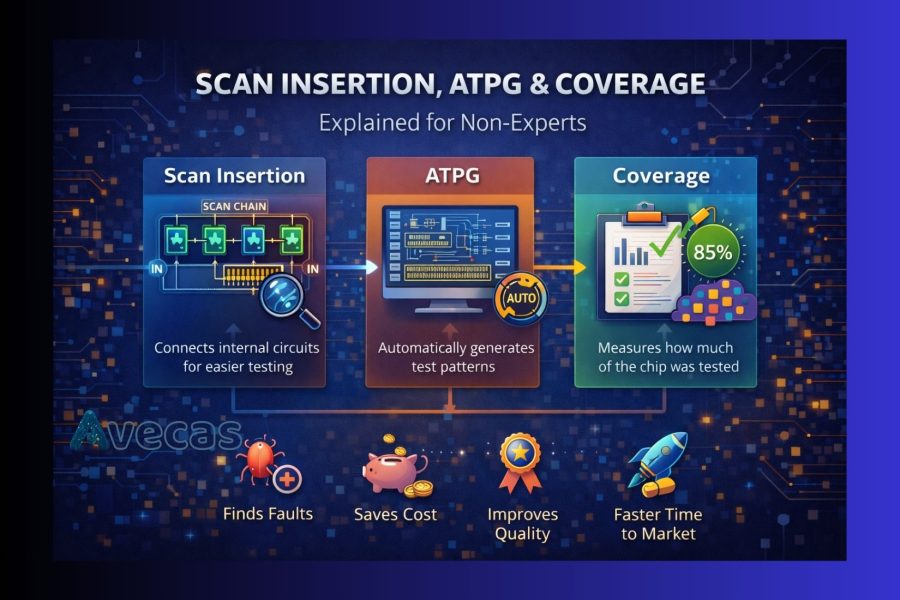

Three key concepts in DFT are scan insertion, ATPG, and test coverage. While these terms may sound technical, their core ideas are actually simple. In this article, we explain scan insertion, ATPG, and coverage in plain language, so even non-experts can understand why they matter and how they help ensure reliable electronic devices.

Why Chip Testing Is Important

When chips are manufactured, tiny defects can occur due to variations in materials, temperature, or fabrication steps. These defects may not be visible but can cause functional failures later.

Effective testing helps to:

- Detect faulty chips before shipping

- Reduce product failures in the field

- Improve reliability and customer trust

- Lower long term manufacturing costs

Scan insertion, ATPG, and coverage work together to make chip testing more effective and systematic.

What Is Scan Insertion

Scan insertion is a technique used to make internal parts of a chip easier to test.

Inside a chip, data moves through many registers called flip-flops. In normal operation, these flip-flops are hard to observe or control directly. Scan insertion connects these flip-flops into long chains, called scan chains, that allow test data to be shifted in and out of the chip.

Simple Explanation

Think of it like opening access points inside a locked building so inspectors can check every room.

Why Scan Insertion Is Needed

- It improves visibility of internal signals

- It allows engineers to control internal states

- It makes fault detection more accurate

Without scan insertion, testing would be limited to external inputs and outputs, missing many internal defects.

What Is ATPG

ATPG stands for Automatic Test Pattern Generation.

Simple Explanation

ATPG is a software process that automatically creates test patterns used to detect faults in a chip. These patterns are sequences of ones and zeros applied to the scan chains to trigger potential defects.

In simple terms, ATPG figures out the best questions to ask the chip so that hidden problems reveal themselves.

What ATPG Does

- Analyzes the chip design

- Identifies possible fault locations

- Generates test patterns to detect those faults

- Optimizes test time and efficiency

ATPG removes the need for manual test creation, saving time and reducing errors.

What Is Test Coverage

Test coverage measures how much of the chip design has been tested.

Simple Explanation

Coverage answers the question, how much of the chip did we actually test.

If coverage is high, it means most potential faults have been checked. If coverage is low, some areas of the chip may still contain undetected issues.

Types of Coverage

- Fault coverage, percentage of detectable faults tested

- Scan coverage, percentage of flip-flops included in scan chains

- Functional coverage, how well real operating scenarios are tested

Higher coverage means greater confidence in chip quality.

How Scan Insertion, ATPG and Coverage Work Together

These three concepts are tightly connected:

- Scan insertion makes internal signals accessible

- ATPG uses that access to generate effective test patterns

- Coverage measures how successful those patterns are

If scan insertion is poor, ATPG effectiveness drops. If ATPG patterns are weak, coverage remains low. All three must work together to achieve reliable testing.

Why These Concepts Matter in Real Products

In real world applications, poor testing can lead to:

- Device failures after deployment

- Costly recalls and replacements

- Damage to brand reputation

- Safety risks in automotive or medical systems

By using scan insertion, ATPG, and coverage analysis, semiconductor companies ensure only high quality chips reach customers.

Benefits of Good Scan and ATPG Strategy

A strong DFT strategy provides several advantages:

- Early detection of manufacturing defects

- Reduced testing time and cost

- Higher yield and better product reliability

- Faster time to market

- Compliance with industry quality standards

These benefits are critical for modern chips used in AI, automotive, IoT, and industrial systems.

Common Misunderstandings for Beginners

Some non-experts believe testing is only about checking if a chip works once. In reality:

- Chips must be tested under many conditions

- Internal signals matter as much as external behavior

- High coverage is essential for long term reliability

Understanding scan insertion, ATPG, and coverage helps clarify why testing is a continuous and detailed process.

Conclusion

Scan insertion, ATPG, and coverage may sound complex, but their purpose is simple, to ensure chips work reliably in the real world. Scan insertion opens access to internal logic, ATPG creates smart test patterns, and coverage measures how well those tests protect against defects.

Together, they form the backbone of modern semiconductor testing. Even for non-experts, understanding these basics provides valuable insight into how high quality electronic devices are built, tested, and trusted.