For decades, the relentless pursuit of Moore’s Law meant packing more and more transistors onto a single, monolithic piece of silicon. This “System-on-a-Chip” (SoC) approach delivered incredible gains. But today, at the bleeding edge of process nodes, the economics are breaking down. The cost of a new tape-out is astronomical, and yields for massive, complex dies are challenging.

So, is the era of scaling over? Not quite. It’s just changing form. The industry is pivoting from a philosophy of monolithic integration to heterogeneous integration. The hero of this new strategy? The Chiplet.

At Avecas Technologies, we’re at the forefront of this architectural shift, helping our clients navigate the complexities of chiplet-based design to build superior products. Let’s break down what this means.

The Problem: The SoC Scaling Wall

Shrinking transistors further is becoming prohibitively expensive. A single mask set for a 3nm node can cost over $100 million. Designing a massive, monolithic SoC at this node is a high-stakes gamble. A tiny flaw anywhere on the die can render the entire chip useless, leading to poor yield and massive financial loss.

This has created a need for a more scalable, cost-effective, and flexible approach.

The Solution: Think Small, Then Integrate

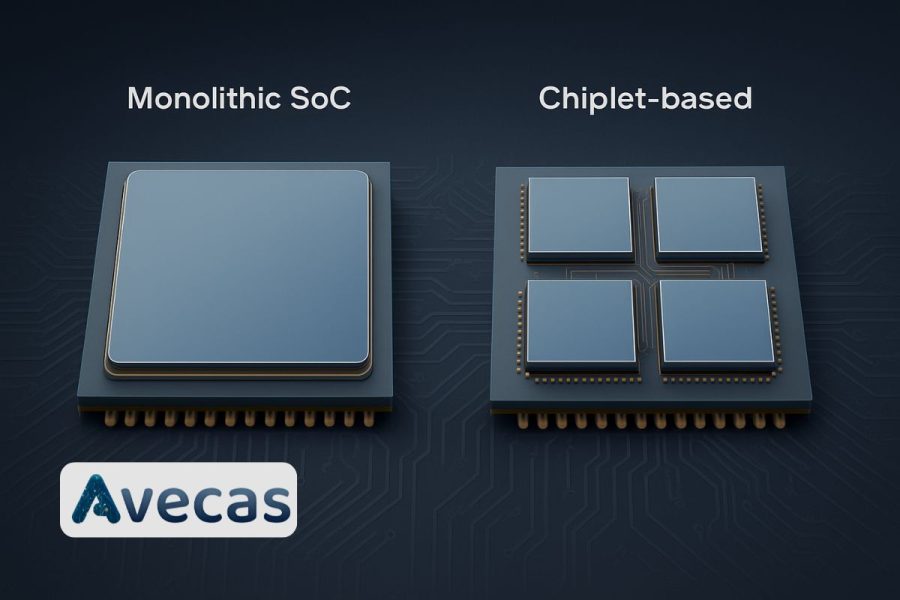

Instead of building one giant die, the chiplet model involves designing a set of smaller, modular dies—each optimized for a specific function and process technology—and then integrating them tightly into a single package.

Think of it like building with LEGO blocks instead of carving a statue from a single piece of marble.

- Monolithic SoC: One large die containing CPU, GPU, I/O, memory controllers, and AI accelerators, all built on the same process node.

- Chiplet-Based Design: A package containing:

- A 5nm CPU chiplet for maximum performance.

- A 6nm GPU chiplet for graphics.

- A 12nm I/O chiplet for connectivity (it doesn’t need an advanced node).

- A stack of HBM memory on the side.

This is the essence of Heterogeneous Integration (HI).

Key Technologies Enabling the Chiplet Revolution

This isn’t possible without breakthroughs in packaging and interconnect technologies.

- Advanced Packaging: This is the foundation. Techniques like 2.5D and 3D Integration allow us to place chiplets side-by-side or stack them on top of each other.

- 2.5D: Chiplets are placed side-by-side on a silicon interposer—a passive layer that provides extremely dense wiring to connect them. This is widely used for high-performance computing (HPC) and GPUs.

- 3D: Chiplets are stacked vertically and connected using microscopic copper pillars called Through-Silicon Vias (TSVs). This allows for incredibly short, fast, and power-efficient connections between, for example, a processor and a memory die.

- Standardized Die-to-Die Interconnects: For chiplets from different vendors to work together, they need a common language. This is where emerging standards like UCIe (Universal Chiplet Interconnect Express) come in. UCIe aims to be the PCIe for chiplets, defining a standard for how chiplets communicate within a package, which is critical for a healthy ecosystem. You can learn more about this standard on the UCIe Consortium website.

The Tangible Benefits of a Chiplet Strategy

Why is the entire industry moving in this direction? The advantages are compelling:

- Improved Yield and Cost: Smaller dies have significantly higher manufacturing yields. You can mix and match chiplets from different process nodes, using expensive advanced nodes only where absolutely necessary, saving huge costs.

- Best-of-Breed Performance: You are no longer locked into a single process technology. You can pair a leading-edge CPU chiplet from Foundry A with a best-in-class analog/RF chiplet from Foundry B.

- Faster Time-to-Market and IP Reuse: Companies can create product families by reusing validated chiplets (e.g., a common I/O chiplet) and simply swapping out a processing chiplet. This dramatically reduces design and verification time. This approach aligns perfectly with our ASIC Design and Implementation services, where IP reuse is a key efficiency driver.

- Unprecedented Flexibility: It enables the creation of systems that would be impossible monolithically, such as stacking memory directly on top of a processor to create a massively bandwidth-rich architecture.

The Challenges and How to Overcome Them

This new paradigm is not without its hurdles:

- Design Complexity: Managing multiple dies, interconnects, and advanced packaging rules adds layers of complexity to the design flow. It requires a deep understanding of system architecture, thermal management, and signal integrity.

- Testing: How do you test individual chiplets before integration? How do you test the fully assembled package? This requires innovative DFT (Design-for-Test) strategies.

- Standards and Ecosystem: While UCIe is a huge step forward, the ecosystem is still maturing.

This is where a partner like Avecas Technologies becomes invaluable. Our expertise in Physical Design and DFT is crucial for navigating the intricacies of multi-die integration, ensuring robust and testable chiplet-based designs.

Conclusion: The Future is Heterogeneous

The move to chiplet architecture and heterogeneous integration is more than a trend; it’s a fundamental restructuring of how we design and build semiconductors. It marks a shift from the era of geometric scaling (smaller transistors) to the era of functional scaling (smarter integration).

It promises a future of more powerful, efficient, and customized silicon, from data center CPUs to specialized AI accelerators.

Is your next design ready to go modular? Embracing this future requires expertise and experience. Contact Avecas Technologies today to discuss how we can help you leverage chiplet architecture to build a competitive advantage and lead the market.