The semiconductor industry is currently navigating its most significant paradigm shift since the introduction of Logic Synthesis in the 1980s. As we push the boundaries of 2nm and 3nm process nodes, the sheer complexity of modern Integrated Circuits (ICs) has outpaced human-centric design methodologies. We are no longer just designing chips; we are managing massive, multi-dimensional data ecosystems.

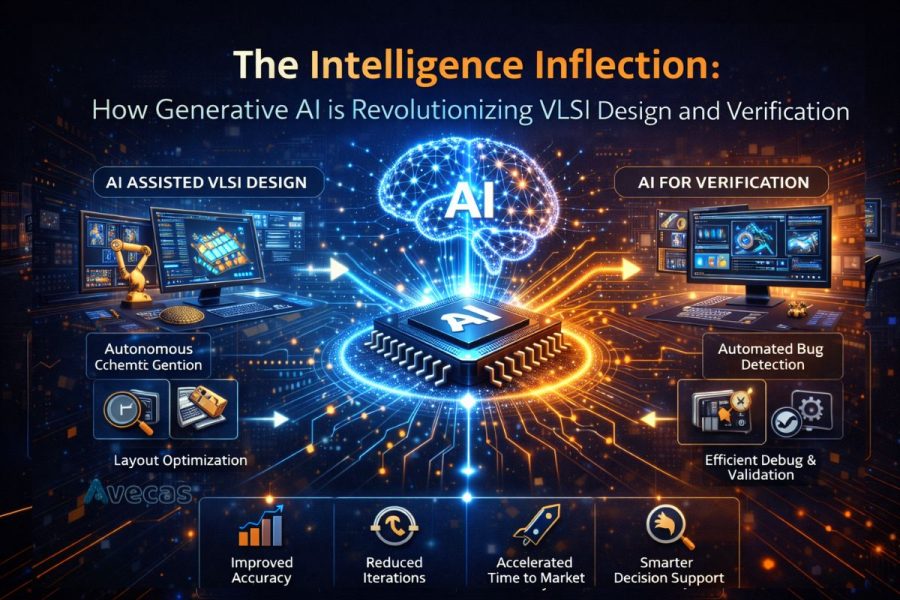

The arrival of Generative AI and advanced Machine Learning (ML) in the VLSI (Very Large Scale Integration) sector is not just an incremental improvement, it is an intelligence inflection point. By automating the most labor-intensive aspects of the design cycle, AI is enabling semiconductor services firms to achieve what was previously impossible: higher performance, lower power consumption, and significantly reduced time-to-market.

Breaking the Productivity Barrier in Design

The traditional IC design flow is a linear, iterative process that requires thousands of engineering hours. From architectural specification to GDSII layout, every step involves complex trade-offs between Power, Performance, and Area (PPA). Historically, optimizing these variables required manual “trial and error” by highly experienced engineers.

Today, AI-driven EDA (Electronic Design Automation) tools are breaking this productivity barrier. Generative AI models can now explore millions of design configurations simultaneously, identifying optimal layouts that a human engineer might never consider. Whether it is automated floorplanning or intelligent clock-tree synthesis, AI is transforming 6 essential steps in chip development into a more fluid, data-driven journey. This shift allows design teams to focus on high-level architecture rather than getting bogged down in repetitive micro-optimizations.

Revolutionizing Verification: From Random to Intelligent

Verification has long been the “bottleneck” of the semiconductor industry. It is estimated that nearly 70% of a chip’s design cycle is spent on verification, yet “first-time-right” silicon remains an elusive goal for many. Traditional constrained-random testing generates billions of simulation cycles, many of which are redundant and fail to uncover the most critical corner-case bugs.

AI-enhanced DFT (Design for Test) Verification & Validation is changing the game. Machine Learning algorithms can now analyze past simulation data to predict where bugs are likely to hide. By focusing stimulus on these “high-risk” areas, AI-driven verification tools can achieve higher coverage with 10x fewer simulation cycles. For specialized providers of DFT Verification & Validation services, this means the ability to guarantee higher reliability for complex AI and automotive chips, where a single undetected bug can lead to catastrophic failure.

AI in the Physical Realm: Manufacturing and Yield

The impact of AI extends far beyond the digital desktop and into the physical world of semiconductor manufacturing. As we move toward advanced packaging and chiplet-based architectures, the margin for error during the manufacturing process has vanished.

AI models are now used for Optical Proximity Correction (OPC) and predictive maintenance in fabrication plants. By analyzing sensor data from manufacturing equipment in real-time, AI can predict when a machine is likely to drift out of tolerance, preventing costly wafer scraps. Furthermore, during Production Test & Silicon Bring-Up Support, AI-driven analytics help engineers quickly correlate failed test patterns with specific manufacturing defects. This “closed-loop” feedback between design and manufacturing is essential for maintaining profitability in the era of sub-5nm nodes.

Global Strategy and the AI Talent Race

The shift toward AI-driven design is also a geopolitical imperative. As nations strive for technological sovereignty under the umbrella of semiconductor nationalism, the ability to design chips faster and more efficiently has become a competitive edge.

Governments are recognizing that AI is the force multiplier for their local industries. For instance, the India Semiconductor Mission 2.0 is not just about building fabs; it is about fostering an ecosystem where local design houses can leverage AI to compete on a global scale. The mission emphasizes the development of “EDA-as-a-Service,” allowing startups to access high-end, AI-powered tools that were once the exclusive domain of industry giants.

The Future: Autonomous Chip Design?

Are we heading toward a future where AI designs chips autonomously? While we are not there yet, we are entering the era of the “Copilot” for silicon. Engineers are now using Agentic AI toolkits to write RTL code, generate testbenches, and even debug complex timing violations. These AI agents act as an extension of the engineering team, handling the “grunt work” while humans make the strategic architectural decisions.

For semiconductor services providers, this evolution requires a new mindset. The value is no longer in “man-hours” but in “intelligence-hours.” Firms that successfully integrate AI into their workflow will be able to handle more complex projects with smaller, more agile teams.

Conclusion: Embracing the Intelligence Inflection

The integration of Generative AI and Machine Learning into the VLSI flow is the only way to sustain the complexity requirements of the next decade. From the initial architectural phase to final silicon bring-up, AI is the thread that connects every stage of the lifecycle, ensuring that the next generation of AI accelerators, 5G modems, and automotive processors are built with unprecedented precision.

As the industry continues to evolve, the distinction between “software” and “hardware” design is blurring. The most successful semiconductor companies will be those that view AI not as a threat to engineering talent, but as the ultimate tool for unlocking human creativity.