Quantum Chips vs Classical Silicon – What to Expect Next?

The semiconductor industry is standing at a major inflection point. For decades, classical silicon chips have powered every digital breakthrough, from personal computing to artificial intelligence and autonomous systems. Today, quantum chips are emerging as a new computing paradigm that promises to solve problems far beyond the reach of conventional processors. Rather than replacing silicon […]

Low-Power SoC Design Techniques for AI and IoT Chips

As AI and IoT devices become part of everyday life, power efficiency has emerged as one of the most critical challenges in modern semiconductor design. From smart wearables and edge AI cameras to industrial IoT sensors, today’s chips must deliver high performance at extremely low power consumption. This is where low-power SoC (System-on-Chip) design plays […]

How Expert VLSI Design Services Improve First-Silicon Success Rate

In the semiconductor industry, achieving first-silicon success is one of the most critical milestones in a chip development project. First-silicon success means that a chip functions as intended during its first fabrication run, without requiring costly re-spins. With rising mask costs, shrinking geometries, and increasingly complex SoCs, the margin for error has become extremely small. […]

In-House vs Outsourced VLSI Design: Cost and Risk Comparison

As semiconductor products become more complex and time-to-market pressures increase, companies face a crucial strategic decision: should VLSI design be handled in-house or outsourced to external partners? Both approaches have distinct advantages, costs, and risks. The right choice depends on business goals, technical requirements, timelines, and long-term scalability. Understanding the trade-offs between in-house and outsourced […]

ASIC vs SoC Design: Choosing the Right Architecture for Your Product

In today’s fast-moving semiconductor industry, choosing the right chip architecture can define the success or failure of a product. Two of the most common and often confused design approaches are ASIC (Application-Specific Integrated Circuit) and SoC (System on Chip). While both are custom silicon solutions, they serve different purposes, budgets, and product goals. Understanding the […]

How Defence & Aerospace Sectors Depend on Indigenous Chip Design

Modern defence capabilities today extend far beyond traditional arms and ammunition. The real battlefield is digital, intelligent, and interconnected. From drones and satellites to missile systems and radar networks, every sophisticated defence platform relies on the silent force inside it: semiconductor chips. These chips operate as the central brain, enabling computation, sensing, navigation, communication, and […]

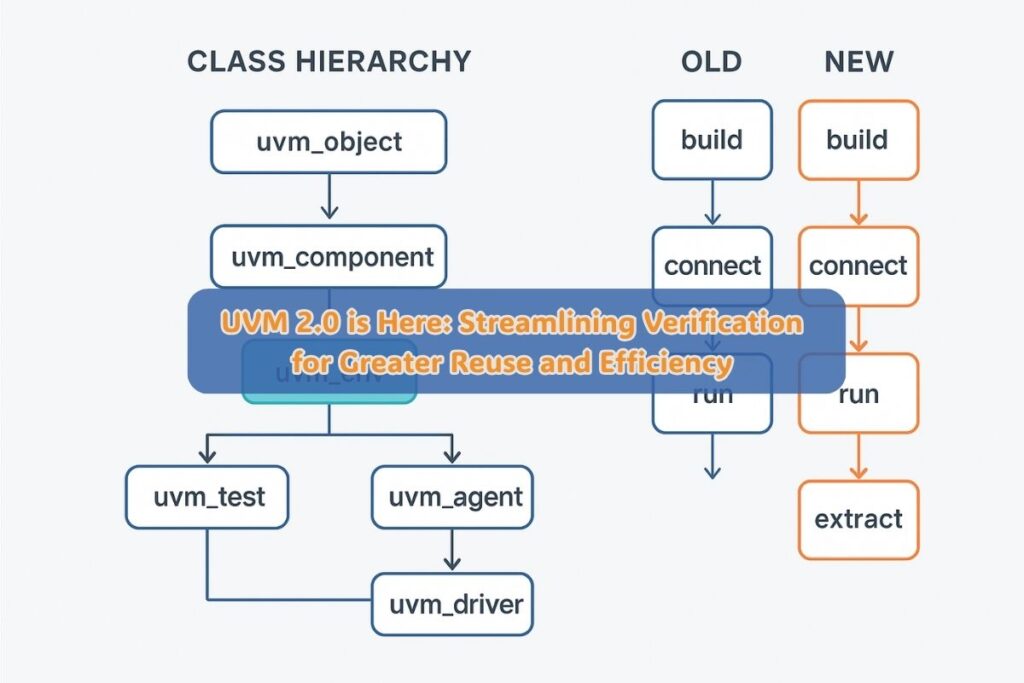

UVM 2.0 is Here: Streamlining Verification for Greater Reuse and Efficiency

The Accellera UVM 2.0 standard is finally here! Discover the key new features like the Phaser API, uvm_void’ roots, and how they boost verification reuse, debug, and efficiency for your ASIC projects.

Taming the Beast: The Unique Verification Challenges of AI/ML Accelerators

The AI revolution is being built on silicon. From data centers to edge devices, custom Neural Network Accelerators (NNAs) are the engines powering the incredible capabilities of large language models, computer vision, and more. But designing these beasts is only half the battle. Verifying them is a monumental challenge that pushes traditional methodologies to their […]

Shift-Left in Verification: How Emulation & Prototyping Find Bugs Earlier to Save Your Project | Avecas

In the high-stakes race to market for complex SoCs and ASICs, a late-stage bug discovery isn’t just a setback—it’s a potential project killer. A bug found at the tape-out stage can cost millions of dollars in re-spins, not to mention the irreplaceable loss of time and market window. For decades, the traditional verification flow has […]

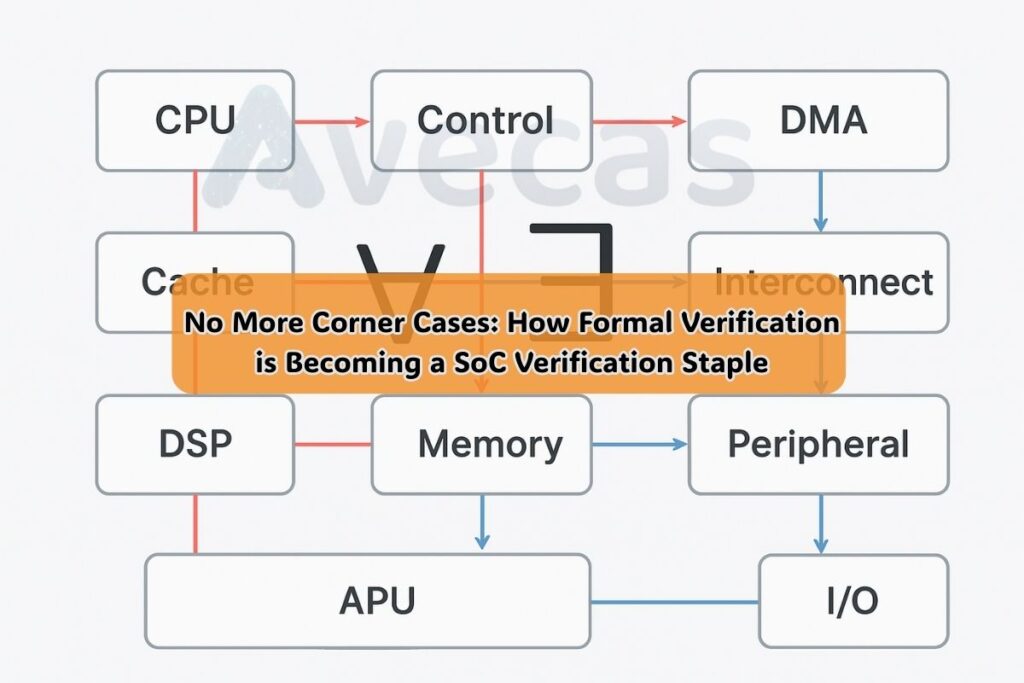

No More Corner Cases: How Formal Verification is Becoming a SoC Verification Staple

For years, the world of ASIC and SoC verification has been dominated by dynamic simulation. We build massive, complex testbenches using UVM, write thousands of tests, and run them for billions of cycles, hoping we’ve thought of every scenario. But what about the corner case you didn’t think of? The rare bug that lurks in a state […]